# 2024 中国研究生创"芯"大赛・EDA 精英挑战赛 赛题指南

## 一、 赛题名称

数字电路仿真中组合逻辑环路分析

#### 二、 命题单位

上海概伦电子股份有限公司

## 三、 赛题主席

祁仲冬(西安电子科技大学)

### 四、 赛题背景

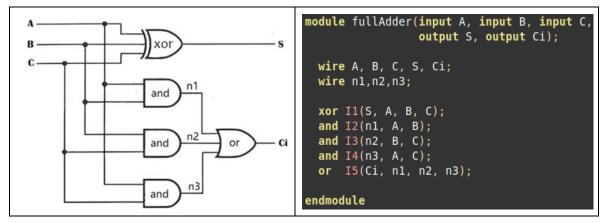

用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、异或门、异或非门等几种。通常门电路为多输入、单输出结构,多个门电路按照一定规则组合在一起可实现具有特定功能的组合逻辑电路,例如下图为 2-bit 带进位全加器的门级电路图和 Verilog 代码。

图 1 2-bit 带进位全加器门电路(左)和 Verilog 代码(右)

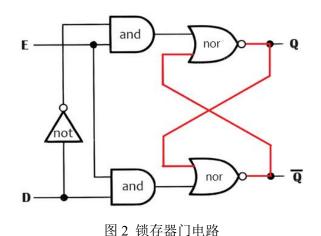

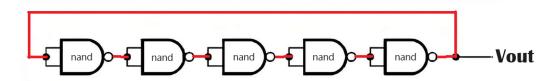

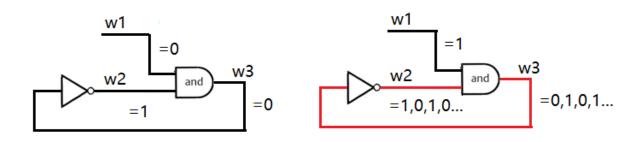

在组合逻辑电路中,起始于某个组合逻辑单元经过一串组合逻辑又回到起始组合逻辑单元的逻辑环路称为组合逻辑环路。组合逻辑环路分为正向反馈和负向反馈两种类型。正向反馈环路是指能够维持当前组合逻辑输出信号状态不变的反馈,常见于锁存器、寄存器和 SRAM 存储器单元等电路中。负向反馈环路是指将当前组合逻辑输出信号翻转的反馈,负向反馈环路会导致输出信号值不停翻转,常见与振荡器、伪随机数生成器等电路中。图 2 和图 3 为锁存器和振荡器门电路,其中红色信号线为锁存器和振荡器门电路中的组合逻辑环路部分。图 4 为不期望的组合逻辑环的示例图,当 w1 为 0 时,w2 为 0,w3 为 1;当 w1 为 1 时,w2 和 w3 将产生震荡。

图 3 由五个与非门构成的震荡器

图 4 不期望的组合逻辑环示例

组合逻辑环路常见于基本的门电路模块中,但在大部分数字电路设计应用场景中都不需要使用组合逻辑环路。不符合预期的组合逻辑环路可能导致多重驱动或信号震荡,导致电路功耗增加和功能错误。组合逻辑环难以被静态时序分析工具分析和计算,可能导致仿真器进入死循环。自动检测数字门电路中的不符合预期的组合逻辑环,分析触发条件和提供断开环路最

小路径,帮助设计人员发现设计问题,是 EDA 工具需要解决的问题。

检测数字门电路中的组合逻辑环路需要获取门电路的拓扑结构和逻辑门信息,可通过 Verilog 仿真器的 VPI 接口实现。 Verilog 语言标准支持使用 VPI(Verilog Procedural Interface)编程语言接口与 C 语言程序交互, VPI 接口提供了一套 C 语言函数,通过这些 C 语言函数可以获取 Verilog 网表的器件连接关系和行为逻辑,并且可访问和修改仿真阶段的信号值。所有 Verilog 仿真器都支持 VPI 接口,在仿真器仿真阶段,通过 VPI 接口可获取网表中逻辑门及其信号连接信息,通过这些信息可构建完整逻辑门电路信息。

#### 五、 赛题描述

给定一个 Verilog 门级网表测试用例,在测试用例中的逻辑门器件中,非门为单输入单输出端口,其他逻辑门均为双输入单输出端口。按 Verilog 语句定义的从左到右顺序,第一个端口为逻辑门的输出端口,其他端口均为逻辑门的输入端口。测试用例中可能包含多个组合逻辑环,并且存在嵌套环的情况。参赛队需编写程序,通过仿真器 VPI 接口获取测试用例中逻辑门及连接信息,通过自定义数据结构构建网表信息,按照赛题要求,运行程序并输出结果。第一至四题的结果需由参赛队提供

程序根据输入的测试用例输出结果文件,第五题为开放式题目,可提供word或PDF文档描述,需要包含示例分析。

● 赛题一:找出测试用例中所有组合逻辑环。

每个组合逻辑环结果应包含信号名称和逻辑门名称两部分,请将结果输出到名为"result 1.txt"文件中。

信号名输出格式以"Loop Signals:"为行首标识,按字典升序输出单个逻辑环中全部信号名称,格式为:

Loop Signals: SignalNameA, SignalNameB, ..., GateNameN

逻辑门名称输出格式以"Loop Gates:"为行首标识,按 字典升序输出单个逻辑环中全部逻辑门名称和输入端口,格式 为:

Loop Gates: GateName1.port#, GateName2.port#, ...,

#### GateNameN.port#

其中"#"为逻辑门的端口序号,按 verilog 语句从左到右顺序从 0 开始编号。通常逻辑门只有一个输出端口,因此无需指定输出端口。

具体输出格式可参考文档第八节的测试用例和参考答案。

● 赛题二:找出不可能发生持续震荡(震荡发生的条件是负反馈)的组合逻辑环。

组合逻辑环的输出格式与1)相同,请将结果输出到名为

"result\_2.txt" 文件中。

● 赛题三:找出可能产生持续震荡的组合逻辑环发生震荡的条件。

输出可能产生持续震荡的组合逻辑环(格式与赛题一相同),并给出要产生持续震荡时逻辑门输入端口必须的逻辑值。请将结果输出到名为"result 3.txt"文件。

逻辑门输入端口逻辑值的格式以"Loop Condition"为行首标识,按字典升序输出。格式为:

Loop Condition: GateName1.port#=0|1, GateName2.port#=0|1, ..., 其中 "#"为逻辑门的端口序号。第 0 号端口是输出端口,因此#为 大于 0 的整数。

● 赛题四:插入最少寄存器断开组合逻辑环。

在第三题的基础上,为了避免组合逻辑环震荡所导致的副作用,可以插入寄存器来打断这些组合逻辑环。

寻找插入最少寄存器的解决方案,输出内容包括需要断开的信号名和插入寄存器后前后连接的逻辑门名称,请将结果输出到名为"result 4.txt"文件中。

假设 GateName1.port#与 GateName2.port#之间通过信号 SignalNameA 连接,要通过插入寄存器断开这两个门的连接,则输出格式为: "Loop Breaker: GateName1.port# - SignalNameA –

Register – SignalNameA' – GateName2.port#'.

#### ● 赛题五:变换并简化逻辑环,能够检测震荡是否发生。

虽然插入寄存器可以打断组合逻辑环从而避免副作用,但被打断后的组合逻辑环与原来的信号逻辑并不等价。例如原本会震荡的组合逻辑由于不会再震荡,从而失去了发现电路中潜在问题的机会;或者需要多次迭代才会稳定的电路被打断后,只能输出一次迭代的结果。请设计一个等价变换,使得变换后的电路既不会震荡,又能得到正确的结果,并且当原组合逻辑环震荡时还可以被检测出来。本赛题为开放式题目,赛题结果可通过文档描述和程序运行结果给出。本题相关的文档名需要以"result\_5"为前缀,例如"result\_5.pdf"、"result\_5.txt"等。

## 赛题提供资料包括:

- 1. 用于获取门级网表电路信息的 VPI 接口示例代码。参赛队在比赛初期可基于开源 Verilog 仿真器 iverilog 的 VPI 接口或其他解析 Verilog 网表套件方式进行开发,最终比赛环境为基于VeriSim 数字仿真器的 VPI 接口运行程序。

- 2. 为方便参赛队开发和测试,提供多个逻辑门数量不同的测试用例示例。最终比赛时使用的测试用例仅包含示例测试用例的器件类型,在比赛阶段提供。

## 六、 评分标准

1. 参赛作品成绩由创新得分和多个测试用例得分的加权和相加得出。每个测试用例得分由精度得分、性能得分组成。第 1~4 题为精度题目,第5 题为创新题目。

$$\begin{aligned} \textit{FinalScore} &= \sum_{t} (\textit{AccuracyScore}_{t} * \textit{wa}_{t} + \textit{PerformScore}_{t} * \textit{wp}_{t}) \\ &+ \textit{InnovateScore} \end{aligned}$$

$$AccuracyScore_{t} = \sum_{q=1}^{4} \left(20 * \frac{C_{q}}{S_{q}} - 5 * \frac{E_{q}}{S_{q}}\right)$$

$PerformScore_t$

$$= \begin{cases} \max \left(0, 10 - log_2\left(\frac{Runtime_t}{BestRunTime_t}\right)\right), & AccuracyScore_t \geq 50\\ 0, & AccuracyScore_t < 50 \end{cases}$$

其中, t 为测试用例序号,

$wa_t$ 和 $wp_t$ 分别是第t个测试用例的精度得分权重和性能得分权重;

q 为题目编号;

$S_q$ 、 $C_q$ 和 $E_q$ 分别为第 q 题全部正确结果数量、参赛作品输出的正确结果数量和输出的错误结果数量;

$Runtime_t$ 是参赛作品当前测试用例的运行时间;  $BestRunTime_t$ 是该测试用例第  $1\sim4$  题得分和超过 50 的所有参 赛作品中运行时间最短的时间。

2. 每个测试用例的程序运行时间超过1小时后将被强制终

- 止,成绩按最终程序输出内容计分。

- 3. 比赛用测试用例按规模分为大、中、小三类,精度得分权重分别为 0.7、0.2 和 0.1,性能得分权重分别为 0.9、0.1 和 0。每类 case 包含 1~3 个测试用例。

### 七、 参考资料

- [1] http://www.asic-world.com/verilog/pli6.html#Verilog\_Procedural\_Interface\_(VPI)

- [2] https://www.runoob.com/w3cnote/verilog2-pli-intro.html

#### 八、 附件

附件提供了一个示例门级网表测试用例和赛题参考答案。

```

1 module combLogic( w_0_0, w_0_1, w_0_2, w_0_3, w_5_0, w_5_1, w_5_2 );

inout w 0 0, w 0 1, w 0 2, w 0 3;

output w 5 0, w 5 1, w 5 2;

wire w 0 0, w 0 1, w 0 2, w 0 3;

wire w 1 0, w 2 0, w 4 0;

wire w 5 0, w 5 1, w 5 2;

I1 0(w 1 0, w 0 0);

8

I1 2(w 1 1, w 0 3, w 0 1);

9

or

I2 0(w 2 0, w 1 0, w 0 1);

10

nand I2 1(w 2 1, w 0 2, w 1 1);

11

nand I4 0(w 4 0, w 2 0, w 0 1);

12

1(w 0 3, w 2

1, w 0 2);

13

nand I5 0(w 5 0, w 4 0, w 0 2);

nand I5 1(w 5 1, w 2 0, w 4 0);

14

15

I5 2(w 5 2, w 0 3);

I6_0(w 0 0, w 5 0);

17 endmodule

```

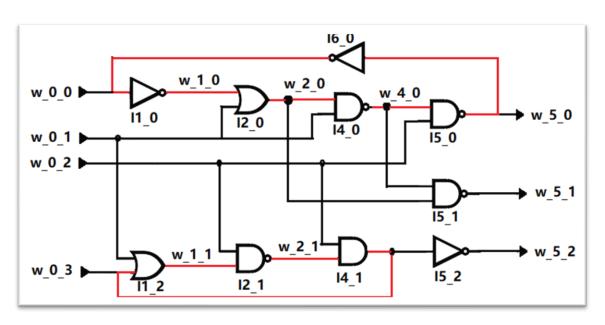

图 5 门级网表 Verilog 代码

图 6 门级网表电路图

图 5 和图 6 分别为示例门级网表的 Verilog 代码和电路图, 赛题参考答案如下。

● 赛题一:找出所有的组合逻辑环。

文件 result 1.txt 中内容如下:

1)

Loop Signals:  $w_0_0$ ,  $w_1_0$ ,  $w_2_0$ ,  $w_4_0$ ,  $w_5_0$

Loop Gates: I1\_0.port1, I2\_0.port1, I4\_0.port1, I5\_0.port1, I6\_0.port1

2)

Loop Signals: w\_0\_3, w\_1\_1, w\_2\_1

Loop Gates: I1\_2.port1, I2\_1.port2, I4\_1.port1

赛题二:找出不可能发生持续震荡(震荡发生的条件是负反馈)的组合逻辑环。

文件 result 2.txt 中内容如下:

1)

Loop Signals: w\_0\_0, w\_1\_0, w\_2\_0, w\_4\_0, w\_5\_0

Loop Gates: I1\_0.port1, I2\_0.port1, I4\_0.port1, I5\_0.port1, I6\_0.port1

● 赛题三:找出可产生持续震荡的组合逻辑环的组合逻辑电路 输入信号值。

文件 result 3.txt 中内容如下:

1)

Loop Signals: w\_0\_3, w\_1\_1, w\_2\_1

Loop Gates: I1 2.port1, I2 1.port2, I4 1.port1

Loop Condition: I1 2.port1=0, I2 1.port1=1, I4 1.port1=1

● 赛题四:插入最少寄存器断开组合逻辑环。

文件 result 4.txt 中内容如下:

1)

$Loop\ Breaker:\ I1\_2.port0-w\_1\_1-Register-w\_1\_1'-I2\_1.port2$

赛题五:设计等价变换,能够检测出震荡,能够简化逻辑环。

略。(可参考相关文献)。

\* 本赛题指南未尽问题, 见赛题 O&A 文件